Ona lortzekoPCB Diseinua, bideratze-diseinu orokorrez gain, linearen zabalera eta tartea egiteko arauak ere funtsezkoak dira. Hori da lerroaren zabalera eta tarteak zirkuituaren taularen errendimendua eta egonkortasuna zehazten dituelako. Hori dela eta, artikulu honetan diseinu orokorreko arau orokorraren aurkezpen zehatza eskainiko da PCB linearen zabalera eta tartea egiteko.

Garrantzitsua da kontuan hartzea software lehenetsitako ezarpenak behar bezala konfiguratu behar direla eta diseinuaren araua (DRC) aukera eman behar dela bideratu aurretik. Gomendagarria da bideratzeko 5mil sareta erabiltzea, eta luzera berdineko 1mil sareta egoeran oinarrituta ezar daiteke.

PCB Linearen zabalera arauak:

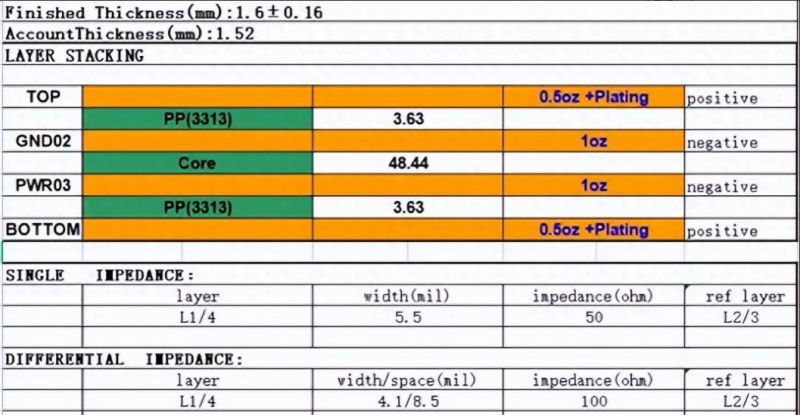

1.Routing-ek lehenik eta behin bete beharko lukeFabrikazio gaitasunafabrikako. Berretsi ekoizpen fabrikatzailea bezeroarekin eta zehaztu haien ekoizpen gaitasuna. Bezeroak baldintza zehatzik ematen ez badu, ikus Linearen zabalera lortzeko inpedantzia diseinatzeko txantiloiak.

2.PalkiduraTxantiloiak: Bezeroak emandako taularen lodiera eta geruzaren eskakizunak oinarritzat hartuta, hautatu inpedantzia eredu egokia. Ezarri lerroaren zabalera inpedantzia-ereduaren barruan kalkulatutako zabaleraren arabera. Inpedantzia-balio arruntak 50ω bakarrekoak dira, 90ω, 100ω diferentziala, eta abar. Kontuan izan 50ω antena seinaleak aldameneko geruzaren erreferentzia izan behar duen ala ez. PCB geruza arruntetarako beheko erreferentzia gisa.

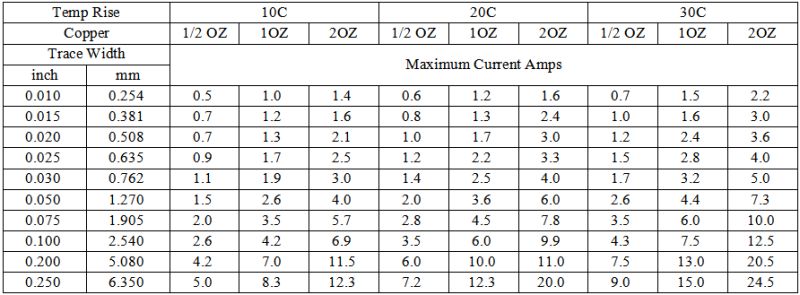

3. Beheko diagraman agertzen diren diagraman agertzen da, linearen zabalerak uneko eramateko gaitasun baldintzak bete beharko ditu. Oro har, bideratze-marjinak kontuan hartuta, Power Line zabalera diseinua kontuan hartuta, jarraibide hauek zehaztu daitezke: 10 ºC-ko tenperatura igoerarako, 1oz kobraren lodiera, 20mil lerroko zabalera 1A-ren gainkarga bat kudeatu dezake 1A-ren gainkargak; 0,5ozko kobrearen lodierarako, 40 milioi lerroko zabalera 1A-ren gainkarga korrontea kudeatu dezake.

4. Diseinu orokorreko helburuetarako, lerroaren zabalera 4mil gainetik kontrolatu behar da, gehienetan fabrikazio gaitasunak bete ditzakeenaPCB fabrikatzaileak. Inpedantziaren kontrola beharrezkoa ez den diseinurako (gehienetan 2 geruzako oholak), 8mil baino gehiagoko lerro zabalera diseinatzeak PCBaren fabrikazio kostua murrizten lagun dezake.

5. kontuan hartuKobre lodierabideratzean dagokion geruza ezarpena. Hartu 2oz kobrea adibidez, saiatu lerroaren zabalera 6milo gainean diseinatzen. Kobrea lodiagoa, lerro zabalera zabalagoa. Eskatu fabrikazioaren fabrikazio baldintzak kobrearen lodiera ez dutenen diseinuak.

6. 0,5mm eta 0,65mm-ko altuerako bga diseinuetarako, 3,5mil lerroko zabalera erabil daiteke zenbait arlotan (diseinu arauen bidez kontrolatu daiteke).

7. HDI BoardDiseinuek 3mil lerroko zabalera erabil dezakete. Linearen zabalerak 3mil azpitik dauden diseinurako, beharrezkoa da fabrikaren produkzioaren gaitasuna bezeroarekin, fabrikatzaile batzuek 2mil linearen zabalerak soilik gai direla (diseinu arauen bidez kontrolatu daitekeena). Lerro meheen zabalerak fabrikazio kostuak handitzen ditu eta ekoizpen zikloa luzatzen du.

8. Seinale analogikoak (audio eta bideo seinaleak esaterako) lerro lodiagoak diseinatu beharko lirateke, normalean 15mil inguruan. Espazioa mugatua bada, lerroaren zabalera 8milo baino gehiago kontrolatu behar da.

9. RF seinaleak lerro lodiagoak izan behar dira, aldameneko geruzei eta 50 urterekin kontrolatutako inpedantziari erreferentzia eginez. RF seinaleak kanpoko geruzetan prozesatu behar dira, barneko geruzak saihestuz eta via edo geruzaren aldaketak erabiltzea minimizatuz. RF seinaleak lurreko plano batez inguratuta egon behar dute, erreferentziako geruza GND kobrea izanik.

PCB kableatzeko lerroaren tartea

1. Kableak fabrikako prozesatzeko ahalmena bete beharko luke, eta lerro-tarteak fabrikako produkzio gaitasuna bete beharko luke, orokorrean 4 miloi edo gainetik kontrolatuta. 0,5 mm edo 0,65mm arteko tartea duten bga diseinuetarako, 3,5 milaren lerro-tartea erabil daiteke zenbait arlotan. HDI diseinuek 3 milako lerro-tartea aukeratu dezakete. 3 miliaren azpitik dauden diseinuek bezeroarekin fabrikazio fabrikaren ekoizpen gaitasuna berretsi beharko dute. Fabrikatzaile batzuek 2 milioko produkzio gaitasuna dute (diseinu-arlo zehatzetan kontrolatuta).

2. Lerroaren tartearen araua diseinatu aurretik, kontuan hartu diseinuaren kobraren lodiera eskakizuna. 1 ontzako kobrearen truke, 4 miloi edo gehiagoko distantzia mantentzen saiatzen da, eta 2 ontzako kobrearentzat, saiatu 6 miloi edo gehiagoko distantzia mantentzen.

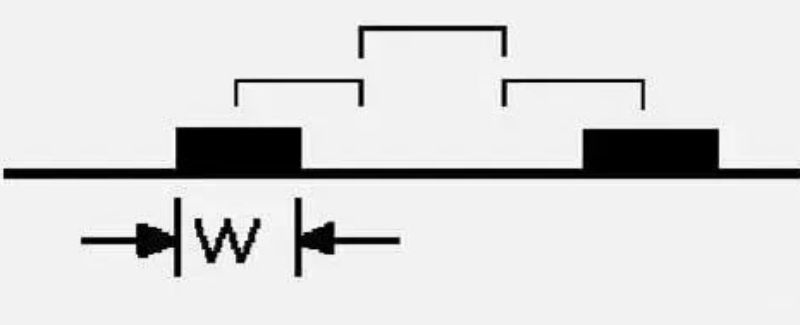

3. Seinale diferentzialen arteko distantzia diseinua ezarri behar da inpedantzia-eskakizunen arabera, tarte egokia ziurtatzeko.

4. Kableak taulako markotik kanpo mantendu behar dira eta saiatu taulako markoak lurrean (GND) vias izan dezakeela ziurtatzen. Mantendu seinaleak eta taulako ertzak 40 milaren gainetik.

5. Potentzia geruzaren seinaleak GND geruzatik gutxienez 10 milako distantzia izan beharko luke. Potentzia eta potentzia kobrezko planoen arteko distantziak gutxienez 10 milako izan behar du. ICS (adibidez, bga) tarte txikiagoarekin, distantzia behar bezala egokitu daiteke gutxienez 6 miliar (diseinu-arlo zehatzetan kontrolatuta).

6. Erlojuak, diferentzialak eta seinale analogikoak bezalako seinaleak 3 aldiz (3W) distantzia izan beharko lukete (3W) edo lurrean (GND) hegazkinez inguratuta egon behar dute. Lerroen arteko distantzia lerroaren zabalera 3 aldiz mantendu behar da crosstalk murrizteko. Bi lerroetako zentroen arteko distantzia lerroaren zabalera 3 aldiz baino txikiagoa bada, marra elektrikoaren% 70 mantendu dezake lerroen arteko interferentziarik gabe, hau da, 3W printzipio gisa ezagutzen dena.

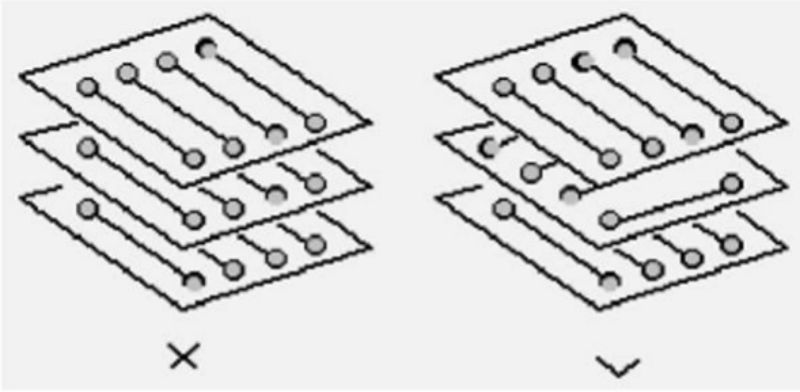

7.Adjako geruza seinaleek kable paralelo paralelo bat ekidin beharko lukete. Bideratze norabideak egitura ortogonala eratu beharko luke, alferrikako interlayer crosstalk murrizteko.

8. Azalera geruza gainean bideratzean, mantendu muntatzeko zulotik gutxienez 1mm-ko distantzia, zirkuitu laburrak edo lerro malkoak saihesteko instalazio estresa dela eta. Torloju zuloen inguruko eremua garbi mantendu behar da.

9. Potentzia geruzak banatzean, saihestu gehiegizko zatitutako zatiketak. Power plano bakarrean, saiatu 5 potentzia seinale baino gehiago, lehentasunez 3 potentzia seinaleen barruan, uneko gaitasuna bermatzeko eta ondoko geruzen planoa zatitutako planoa zeharkatzeko seinalea izateko arriskua ekiditeko.

10.Power Plane Divisions ahalik eta ohikoena izan behar da, luzea edo dumbbell itxurako zatiketak egin gabe, muturrak handiak diren egoerak ekiditeko, eta erdia txikia da. Egungo eramateko ahalmena potentziako kobrezko planoaren zabalera estuenean kalkulatu beharko litzateke.

Shenzhen Anke PCB Co., Ltd

2023-9-16

Posta: 2012ko irailaren 19a